文章图片

文章图片

开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动其吸收电流的能力相对强(一般20ma以内) 。

推挽结构一般是指两个三极管分别受两互补信号的控制总是在一个三极管导通的时候另一个截止 。

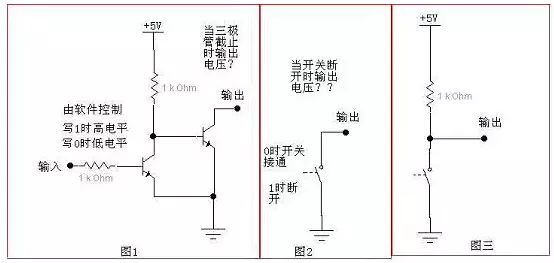

我们先来说说集电极开路输出的结构 。 集电极开路输出的结构如图1所示 , 右边的那个三极管集电极什么都不接 , 所以叫做集电极开路(左边的三极管为反相之用 , 使输入为“0”时 , 输出也为“0”) 。 对于图1 , 当左端的输入为“0”时 , 前面的三极管截止(即集电极C跟发射极E之间相当于断开) , 所以5V电源通过1K电阻加到右边的三极管上 , 右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时 , 前面的三极管导通 , 而后面的三极管截止(相当于开关断开) 。

【cmos|(干货分享)MCU引脚输出模式中推挽输出与开漏输出电路原理区别】

我们将图1简化成图2的样子 。 图2中的开关受软件控制 , “1”时断开 , “0”时闭合 。 很明显可以看出 , 当开关闭合时 , 输出直接接地 , 所以输出电平为0 。 而当开关断开时 , 则输出端悬空了 , 即高阻态 。 这时电平状态未知 , 如果后面一个电阻负载(即使很轻的负载)到地 , 那么输出端的电平就被这个负载拉到低电平了 , 所以这个电路是不能输出高电平的 。

再看图三 。 图三中那个1K的电阻即是上拉电阻 。 如果开关闭合 , 则有电流从1K电阻及开关上流过 , 但由于开关闭其它三个口带内部上拉) , 当我们要使用输入功能时 , 只要将输出口设置为1即可 , 这样就相当于那个开关断开 , 而对于P0口来说 , 就是高阻态了 。

对于漏极开路(OD)输出 , 跟集电极开路输出是十分类似的 。 将上面的三极管换成场效应管即可 。 这样集电极就变成了漏极 , OC就变成了OD , 原理分析是一样的 。

另一种输出结构是推挽输出 。 推挽输出的结构就是把上面的上拉电阻也换成一个开关 , 当要输出高电平时 , 上面的开关通 , 下面的开关断;而要输出低电平时 , 则刚好相反 。 比起OC或者OD来说 , 这样的推挽结构高、低电平驱动能力都很强 。 如果两个输出不同电平的输出口接在一起的话 , 就会产生很大的电流 , 有可能将输出口烧坏 。 而上面说的OC或OD输出则不会有这样的情况 , 因为上拉电阻提供的电流比较小 。 如果是推挽输出的要设置为高阻态时 , 则两个开关必须同时断开(或者在输出口上使用一个传输门) , 这样可作为输入状态 , AVR单片机的一些IO口就是这种结构 。

开漏电路特点及应用

在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念 。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极 。 同理 , 开集电路中的“集”就是指三极管的集电极 。 开漏电路就是指以MOSFET的漏极为输出的电路 。 一般的用法是会在漏极外部的电路添加上拉电阻 。 完整的开漏电路应该由开漏器件和开漏上拉电阻组成 。 如图1所示:

图1组成开漏形式的电路有以下几个特点:

1. 利用外部电路的驱动能力 , 减少IC内部的驱动(或驱动比芯片电源电压高的负载) 。 当IC内部MOSFET导通时 , 驱动电流是从外部的VCC流经R pull-up, MOSFET到GND 。 IC内部仅需很下的栅极驱动电流 。 如图1 。

2. 可以将多个开漏输出的Pin , 连接到一条线上 。 形成 “与逻辑” 关系 。 如图1 , 当PIN_A、PIN_B、PIN_C任意一个变低后 , 开漏线上的逻辑就为0了 。 这也是I2C , SMBus等总线判断总线占用状态的原理 。 如果作为输出必须接上拉电阻 。 接容性负载时 , 下降延是芯片内的晶体管 , 是有源驱动 , 速度较快;上升延是无源的外接电阻 , 速度慢 。 如果要求速度高电阻选择要小 , 功耗会大 。 所以负载电阻的选择要兼顾功耗和速度 。

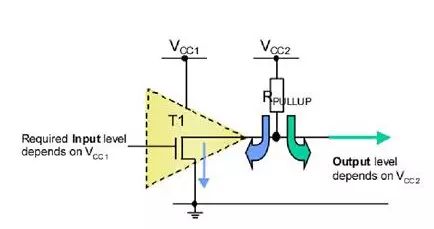

3. 可以利用改变上拉电源的电压 , 改变传输电平 。 如图2 IC的逻辑电平由电源Vcc1决定 , 而输出高电平则由Vcc2(上拉电阻的电源电压)决定 。 这样我们就可以用低电平逻辑控制输出高电平逻辑了(这样你就可以进行任意电平的转换) 。 (例如加上上拉电阻就可以提供TTL/CMOS电平输出等 。 )

- 蓝牙耳机|哪款蓝牙耳机适合学生党? 2021高人气蓝牙耳机分享

- 宜君|经纬张颖最新分享:科研创业代替互联网创业时代,我有9大建议

- 阿里巴巴|多账号运营如何防止关联技巧分享

- 智云|电猴网【11月26日快报】电商资讯/干货,网罗天下电商新鲜事儿

- 苹果|16GB内存,1英寸CMOS,2亿像素,安卓阵营用实力反击iPhone?

- 自媒体|分享实操和方法,听歌也能赚钱,一个月挣了6000多

- 青岛市|干货!抖音直播付费流量撬动自然流量的核心逻辑

- 凯迪仕|圣诞送闺蜜有哪些平价好用的蓝牙耳机?宝藏蓝牙耳机分享

- cmos|长光辰芯研发出4800万像素CMOS,打破美日的联合垄断

- 数字化转型|电猴网【11月23日快报】电商资讯/干货,网罗天下电商新鲜事儿