储器层次结|「计算机组成原理」:高速缓存存储器

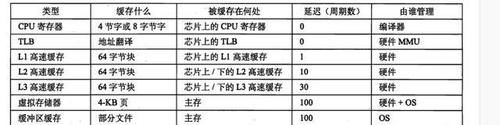

一旦从存储器读入一个数据对象时,就尽可能使用它,使得时间局部性最大。特别是局部变量,编译器会将其保存在寄存器中。 这一章主要介绍存储器层次结构中的高速缓存部分,包含在CPU中,使用SRAM存储器实现,完全由硬件管理。

- 当高速缓存大小大于数据的大小,如果分配良好,则只会出现冷不命中。

- 缓存不命中比内存访问次数影响更大

- 由内存系统的设计来决定块大小,是内存系统的固定参数。首先决定块大小,然后决定期望的缓存大小,然后再决定关联性,最终就能知道组的数目。

- 块的目的就是利用空间局部性

- 缓存是硬件自动执行的,没有提供指令集对其进行操作

- 建议:将注意力集中在内循环中,因为大部分的计算和内存访问都集中在这里按照数据对象存储在内存中的顺序,以步长为1来读数据,使得空间局部性最大。比如步长为2的命中率就比步长为1的命中率降低一半。一旦从存储器读入一个数据对象时,就尽可能使用它,使得时间局部性最大。特别是局部变量,编译器会将其保存在寄存器中。

1 高速缓存存储器

较早期的计算机系统的存储器层次结构只有三层:CPU寄存器、主存和磁盘,但是随着CPU的发展,使得主存和CPU之间的读取速度逐渐拉大,由此在CPU和主存之间插入一个小而快速的SRAM高速缓存存储器,称为L1高速缓存,随着后续的发展,又增加了L2高速缓存和L3高速缓存。

文章插图

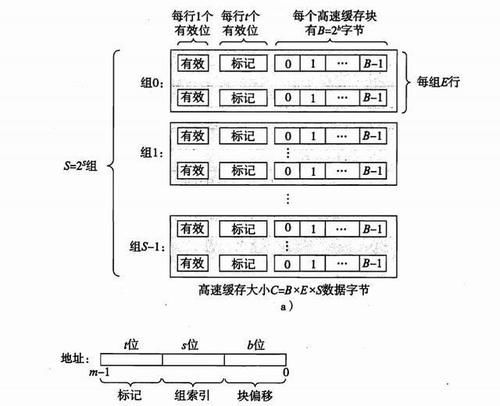

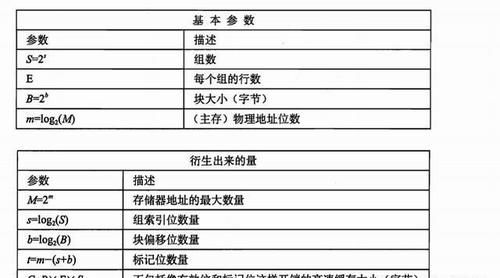

1.1 通用的高速缓存存储器组织结构

文章插图

如上图的b中所示,会将m位的的址划分成三部分:

- s位:高速缓存被组织成一个数组,而该数组通过 $$ S=2^{s} $$ 进行索引。

- b位:每个组中包含E个高速缓存行(Cache Line),每个行有一个 $$ B=2^{b} $$ 字节的数据块(Block)组成。

- t位:每一个高速缓存行有一个 $$ t=m-(s+b) $$ 位的标记位(Valid Bit),唯一表示存储在这个高速缓存行中的数据块,用于搜索数据块。

文章插图

该高速缓存的结构可以通过元组(S, E, B, m)来描述,且容量C为所有块的大小之和, C= S times E times BC=S×E×B。

注意:如果将组索引放在最高有效位,则连续的内存块就会映射到相同的高速缓存组中,通过将组索引放在中间,可以使得连续的内存块尽可能分散在各个高速缓存组中,可以充分利用各个高速缓存组

- 多年养花总结:大蒜能治蚜虫、浇水要控温、换盆可美化株型

- 辅食添加|6月辅食添加总结,最真实的反馈来啦!

- 君王|此人把怀孕妻子送给皇帝,结果却被妻子极其哥哥处死

- 就是|此人想学自己老爹造反称帝,结果却被活活烤死,下场极其悲催

- 女儿|吕布被曹操斩首后,把赤兔马送给关羽,吕布之女结局如何?

- 恭喜!他们结婚了!

- 金弹子不结果,这3大原因造成的,对症下药提高座果率

- 美女带满绿翡翠观音进行鉴宝,纠结嫁妆选观音还是房产?

- 伯温|刘伯温智比诸葛亮,才比萧何张良,可结局却是那么地悲凉!

- 此皇帝因偷国库中的钱,结果朝会时被群臣从龙椅上拖下来痛打20棍