储器层次结|「计算机组成原理」:高速缓存存储器( 四 )

1.2 写操作

当CPU想要对地址A进行写操作时,会通过地址A判断是否缓存了该地址,如果缓存了称为写命中(Write Hit),否则称为写不命中(Write Miss)。

- 写命中:高速缓存会先更新缓存的副本,然后可以采取不同方法更新下一层的副本直写(Write-Though):立即更新下一层的副本值。缺点是每次写都会引起总线流量。写回(Write-Back):为每个高速缓存行维护一个修改位(Dirty Bit),表明这个高速缓存块是否被修改。当被修改的高速缓存块被驱逐时,会查看修改位,判断该块是否被修改,只有被修改才会更新下一层的副本值。能够显著减少总线流量,但是复杂性高。

- 写不命中:写不分配(Not-Write-Allocate):直接将字写到下一层中。写分配(Write-Allocate):加载相应的下一层的块到当前层的高速缓存中,然后更新当前高速缓存块。得益于空间局部性,进行一次写分配后,下一次有较高几率会写命中,但是缺点是每次写不命中就要将块从第一层向上传输。

建议采用写回写分配模型,因为随着逻辑电路密度的提高,写回的复杂性不再成为阻碍,并且和处理读相同,都利用了局部性原理,效率较高。

1.3 真实高速缓存结构

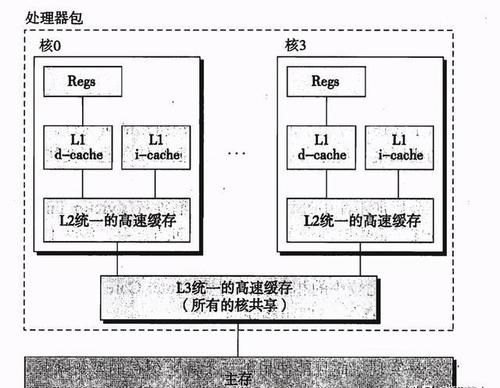

之前介绍的高速缓存值保存程序数据,但是高速缓存同样也能保存指令。可以将高速缓存分成以下几种:

- i-cache:只保存指令的高速缓存

- d-cache:只保存程序数据的高速缓存

- Unified Cache:既能保存指令,也能保存程序数据的高速缓存

文章插图

如上图所示是Intel Core i7的高速缓存层次结构,可以发现在L1高速缓存中分成了L1 d-cache和L1 i-cache,这样做的好处在于:

- 将数据和指令分别保存在两个高速缓存中,使得处理器可以同时读一个指令字和一个数据字

- i-cache通常是只读的,所以会比较简单

- 可以针对不同的访问模式优化这两个高速缓存,使用不同的块大小、相联度和容量

- 确保数据访问和指令访问之间不形成冲突不命中

- 代价就是会导致高速缓存容量变小,提高出现容量不命中的可能性。

衡量高速缓存的指标有:

- 命中率(Hit Rate):内存引用命中的比率,命中数量/引用数量。

- 不命中率(Miss Rate):内存引用不命中的比率,不命中数量/引用数量。通常,L1高速缓存为3~10%,L2高速缓存为<1%。

- 命中时间(Hit Time):从高速缓存传输一个字到CPU的时间,包括组选择、行匹配和字选择时间。通常,L1高速缓存需要4个时钟周期,L2高速缓存需要10个时钟周期。

- 多年养花总结:大蒜能治蚜虫、浇水要控温、换盆可美化株型

- 辅食添加|6月辅食添加总结,最真实的反馈来啦!

- 君王|此人把怀孕妻子送给皇帝,结果却被妻子极其哥哥处死

- 就是|此人想学自己老爹造反称帝,结果却被活活烤死,下场极其悲催

- 女儿|吕布被曹操斩首后,把赤兔马送给关羽,吕布之女结局如何?

- 恭喜!他们结婚了!

- 金弹子不结果,这3大原因造成的,对症下药提高座果率

- 美女带满绿翡翠观音进行鉴宝,纠结嫁妆选观音还是房产?

- 伯温|刘伯温智比诸葛亮,才比萧何张良,可结局却是那么地悲凉!

- 此皇帝因偷国库中的钱,结果朝会时被群臣从龙椅上拖下来痛打20棍